전체 Shcematic 구조는 위 그림과 같다.

간단한 동작 설명을 하면 다음과 같다.

5 to 32 Row Decoder(Active Low) 출력선과 5 to 32 Column Decoder(Active Low) 출력선이 Nor gate에서 만나 WordLine을 1로 만들어 원하는 4비트 셀을 선택한다.

다음으로 Precharge로 읽기/쓰기 동작을 준비하고, Tristate_Buffer_Feedback에 DATA가 들어간다.

쓰기 동작 시 Tristate_Buffer_Feedback에 의해 읽기 동작은 발생하지 않으며, 반대로 읽기 동작 시에는 쓰기 동작은 발생하지 않는다.

읽기 동작 시에는 BL과 BL’의 차이를 Sense_Amp를 통해 읽는다.

이때, Sense_Amp 출력은 Tristate_Buffer_Feedback 출력 부분과 연결되어 DATA가 들어가던 동일한 핀으로 읽습니다.

5 to 32 디코더는 5비트의 입력을 받아서 32개의 출력 중 하나를 선택해서 출력한다.

우리는 2 to 8 디코더와 3 to 8 디코더를 이용해서 구현했다.

1. 입력: 5비트 입력 중에서 상위 2비트와 하위 3비트로 나눈다.

- 상위 2비트: S4, S3

- 하위 3비트: S2, S1, S0

2. 2 to 4 디코더 사용:

- 상위 2비트(S4, S3)는 2 to 4 디코더의 입력으로 사용된다.

- 2 to 4 디코더는 4개의 출력(EN0, EN1, EN2, EN3)을 가지며, 하나만 활성화.

3. 3 to 8 디코더 사용:

- 하위 3비트(A2, A1, A0)는 3 to 8 디코더의 입력으로 사용된다.

- 3 to 8 디코더는 8개의 출력 중 하나만 선택된다.

동작 과정

1. 상위 2비트:

- 상위 2비트(S4, S3)는 2 to 4 디코더의 입력으로 들어가서, 4개의 출력 중 하나를 출력한다.

ex) S4S3 = 00이면 Y0가 활성화되고, S4S3 = 01이면 Y1(0으로)가 출력.

2. 하위 3비트:

- 각 2 to 4 디코더의 출력(EN0, EN1, EN2, EN3)은 각각 3 to 8 디코더의 Enable 입력으로 사용된다.

- 하위 3비트(A2, A1, A0)는 모든 3 to 8 디코더의 입력으로 사용된다.

3. 최종 출력:

- 상위 2비트 디코더의 특정 출력이 활성화되면, 해당 출력에 연결된 3 to 8 디코더가

활성화됩니다.

- 3 to 8 디코더는 하위 3비트에 따라 8개의 출력 중 하나를 활성화합니다.

- 결과적으로 32개의 출력 중 하나만 활성화됩니다.

ex)

만약 입력이 10101 (S4.S3.S2.S1.S0)라고 가정하면,

- 상위 2비트(S4.S3)는 10이므로, 2 to 4 Decoder의 세 번째 출력(EN2).

- EN2가 활성화되면, 세 번째 3 to 8 Decoder가 동작.

- 하위 3비트(S2.S1.S0)는 101이므로, 세 번째 3 to 8 Decoder의 여섯 번째(D21)가 출력.

결과적으로, 5 to 32 디코더의 22번째(D21)이 출력된다.

우리가 5 to 32 Decoder를 Low Decoder로 만든 이유는 다음과 같다.

① 전력 소비 감소

CMOS 회로에서 전력 소비가 Low 상태에서 더 적기 때문에, 전력 소비를 줄일 수 있다.

② 간단한 회로 구조

NAND 게이트와 같은 간단한 논리 게이트를 사용할 수 있다. 회로 설계를 단순화하고, Layout 시 좋다고 생각했다.

2. SRAM 6T Cell

가장 기본적인 SRAM 6T Cell 구조를 사용했다.

Hold Mode(대기 동작)

WL=0일 때, Pass TR이 Off 상태가 되면서 Inverter Latch 회로에서 현재 값이 유지 된다.

2. Read(읽기 동작), Write(쓰기 동작)

데이터를 읽고, 쓰기 위해서는 WL이 1이 되어 있어야 Inverter Latch 회로와 BL, BL’ 라인 까지의 통로가 이어진다.

자세한 건 Write_Driver, Sens_Amp에서 설명하겠다.

SRAM Sizing

SRAM cell의 6개의 transistor의 크기는 N1 > N3 > P1 (N2 > N4 > P2)여야 한다.

SRAM cell에는 2개의 값(A, A_bar 영역)이 저장될 수 있고 두 값은 항상 상반된다.

이때 값이 0이라는 것은 ground에 연결되었다는 것이고, 1이라는 것은 VDD에 연결되었다는 것을 의미한다.

읽기 시, 두 bitlines(BL, BLB)는 모두 1의 상태를 가진다. 이때 cell 내 0인 값을 변화시키면 안된다. 따라서 ground와 연결된 NMOS transistor가 가장 큰 크기를 가진다.

쓰기 시, 두 bitlines(BL, BLB)는 0 또는 1의 상반된 값을 가진다. 이때 cell의 값을 변화시키고 싶으면 cell 내 1인 값을 변화(1->0)시켜야 한다. 그러면 자동으로 0인 값도 1로 변화된다. 따라서 VDD와 연결된 PMOS transistor의 크기가 가장 작아야 한다.

따라서 다음과 같은 Sizing으로 진행하였다.

Pull UP width : 1.6um

Pull Down width : 3um

Pass Transistor width : 2um

3. Nor + SRAM Cell

우리는 1K * 4Bit를 설계해야 하므로 [그림 10]과 같이 총 SRAM 6T Cell 4개를 이어서 Nor gate 출력선과 연결했다.

Nor gate의 A와 B에는 초기에 설명했던 5 to 32 Row Decoder와 5 to 32 Column Decoder의 출력값이 각각 들어와 선택된 4Bit Cell의 Word_Line을 1로 만든다.

이때, Nor gate를 사용한 이유는 Low Decoder이므로 Decoder에서 나온 값이 0이므로 Nor_gate 출력값인 WL이 1이 되기 때문이다

4. Pre_charge (PMOS width : 1.8u)

PRE 신호와 WE 신호가 동일시하게 들어와서 PRE를 WE로 바꿨다.

PRE(WE)를 통해 신호가 들어옴으로써 읽기 동작과 쓰기 동작 준비가 완료된다.

예를 들어, PRE(WE)에 0이 들어오면 3개의 PMOS가 켜지게 되고, BL, BL’가 VDD(5V)와 연결되고, 읽기 동작이 준비된다.

반대로 PRE(WE)에 1이 들어오면 3개의 PMOS가 OFF 상태가 되고, BL, BL’이 Floating 상태로 되며 쓰기 동작이 준비된다.

5. Write_Driver(NMOS width : 3.5u)

Write_Driver는 Data를 쓰는 셀이다.

[그림 14]와 같이 DATA가 들어가면, BL과 BL’이 GND 또는 Floating 2가지 상태로 변한다.

예를 들어, DATA가 0이 들어가면 왼쪽 NMOS가 OFF가 되면서 GND와 연결되며 BL값이 Floating 상태로 바뀐다. 또한, Inverter 출력값은 1이 되고, 오른쪽 NMOS는 ON이 되며 GND 상태가 된다.

이 BL과 BL’ 값에 의해 DATA가 SRAM Cell에 써진다.

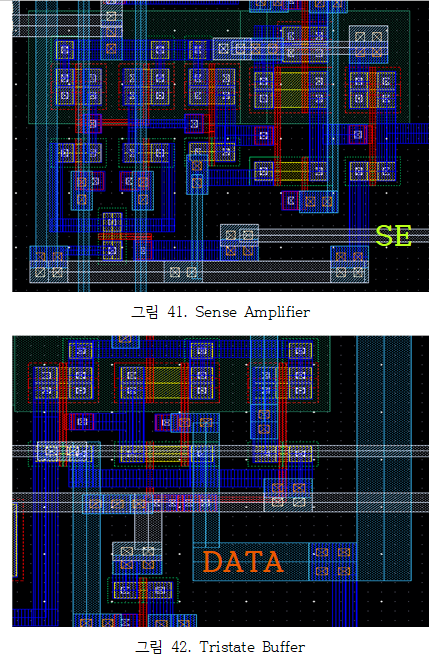

6. Tristate_Buffer(NMOS width : 1.6u, PMOS width : 3.2u)

Tristate_Buffer는 입력핀과 출력핀을 하나로 사용하기에 넣었다.

[그림 16]에서 보는 것처럼 Tristate Inverter와 Inverter를 연결해서 Tristate Buffer를 구현했다.

[그림 17]과 [그림 18]을 보면 Inverter 방향이 서로 다른 것을 볼 수 있다.

DATA가 VIN으로 들어가고 Write 동작 시에는 [그림 16] 위의 Tristate Inverter가 동작하고, 아래의 Tristate Inverter는 동작하지 않는다.

반대로 Read 동작 시에는 [그림 16] 위의 Tristate Inverter가 동작하지 않고, 아래의 Tristate Inverter는 동작한다.

전체 회로로 봤을 때, [그림 16]의 VOUT1은 Write_Driver의 DATA 라인으로 들어가며, VOUT2는 Sense_Amplifier의 출력 RDATA와 연결된다.

이를 통해, 하나의 핀을 이용하여 DATA를 쓰고, 읽을 수 있다.

7. Sense_Ampifier(NMOS width : 1.6u, PMOS width : 3.2u)

Sense_Amplifier는 셀에 저장된 Data를 읽는 역할을 한다.

예를 들어, SRAM Cell 왼쪽 Q 기준으로 1(5V)이 저장되었다고 가정하자. (Q_b는 0)

읽기 동작 시 BL, BL’는 Precharge로 각각 5V를 유지하고 있다, WL이 Decoder에 의해 선택되고, SRAM Cell 왼쪽 Q는 전압 변화가 없어 BL은 5V를 유지하고, BL’는 Q_b=0에 의해 전압 강하가 발생한다.

결과적으로 WE가 0이 되고, SE가 1이 되면서, [그림 20]에서 BL이 들어가는 TR은 켜지게 되고, BL’가 들어가는 TR은 꺼지게 된다. GND와 연결되어 오른쪽 PMOS가 켜지게 되는데, 이는 다시 VDD와 연결되고 이 값은 Inverter를 통해 RDATA에 0을 전달한다.

이는 곧 Q_b에 저장된 값이다.

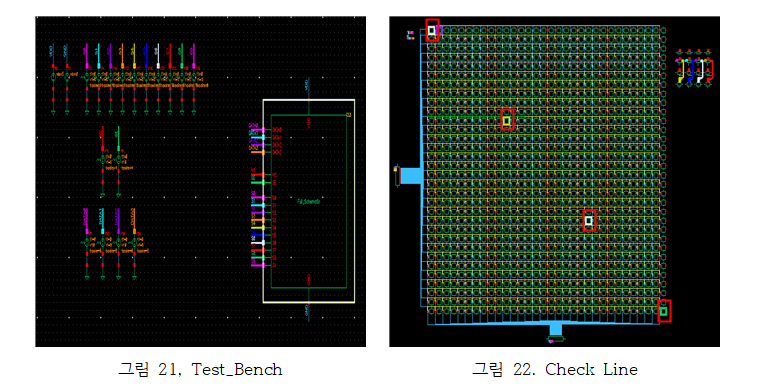

⓶ Simulation

Full Schematic 시뮬레이션을 돌리기 위해 Test_Bench 셀을 만들고, maestro로 output line을 위 그림과 같이 확인했다.

위 그림에서 왼쪽부터 1Bit, 2Bit, 3Bit, 4Bit이며, 셀에 저장된 값을 올바르게 읽는지 확인하기 위해 RDATA 라인들을 선택했다.

결과는 다음과 같다.

잘 쓰고, 읽는 지를 확인하기 위해 4Bit SRAM Cell 1024개 중 랜덤으로 4개를 골랐다.

랜덤 4개는 다음과 같다.

11111 11111 / 10101 10101 / 01010 01010 / 00000 00000

WE가 1일 때, 즉 쓰기 동작이 이루어질 때는 읽기 동작이 이루어지지 않아야 하므로 SE는 0이고, 반대로 읽기 동작일 때는 쓰기 동작이 이루어지지 않아야 하므로 WE가 0일 때, SE가 1이다.

이때, 쓰기 동작에서 읽기 동작으로 변할 때, 약간의 Delay를 줘서 유지 여부를 확인했다.

[그림 24]와 [그림 25]를 같이 보면 WE가 1일 때, 11111 11111([그림 22] 왼쪽 첫 번째 빨간박스) 4Bit Cell 1Bit에 0, 2Bit에 1, 3Bit에 0, 4Bit에 1을 쓰는 것을 확인할 수 있다.

일정 시간이 지나고, WE가 0, SE가 1이 될 때, 똑같이 11111 11111 4Bit Cell을 선택하고 0101을 쓴 값을 그대로 읽어내는 것을 확인했다.

[그림 29] 가장 밑에 초록색이랑 보라색 부분은 [그림 22] 왼쪽 첫 번째 빨간박스 안 Q와 Q_b를 보여준다. 다음 그림을 보면 이해하기 쉽다.

❶ Layout

S0~S9(10개), DATA inout Port 4개 WE, SE, VDD GND를 총 합한 18개의 핀을 사용했다.

핀들의 위치는 [그림 31]과 같고 VDD를 ㄱ자로 배치하였고 GND를 ㄴ자로 배치하여서 모든 소자에 VDD, GND 전압 공급을 원활하게 했다.

Row Decoder와 Column Decoder를 위와 왼쪽에 배치하여 각각 5개 핀을 이용하여 총 10개의 pin을 사용하였고 아래쪽에 DATA 입출력 핀 4개를 사용했다. 마지막으로 WE, SE 신호를 오른쪽 밑에 배치하였습니다.

전체적인 Layout은 [그림 31]과 같다.

그림 안에 표시된 번호 순서대로 설명하겠다.

⓵ Nor + SRAM Cell * 4Bit

⓵을 확대하면 [그림 32]와 같다.

[그림 32]는 Norgate와 SRAM Cell * 4Bit를 16개 붙여놓은 그림이다.

전체 Schematic에서는 Norgate + SRAM Cell * 4Bit가 1024개가 있다.

이를 좀 더 확대해서 SRAM Cell * 4Bit만 보자.

그 그림이 [그림 33]이다.

1K*4Bit의 총 4096bit의 SRAM을 만들기 때문에 Size 문제에 직면할 수밖에 없었다.

그림 34. 6T Cell 1개

하나의 6T Cell을 4가지로 Layout을 진행하였고, 그 4가지를 4bit 셀로 합쳐보았을 때, 세로로 길게 뽑은 Layout이 Norgate까지 붙였을 때 가장 정사각형에 가까웠으므로 이 구조를 선택했다.

하나의 6T Cell Layout은 [그림 34]와 같다.

또한, BL과 BL'의 간격을 4.4um로 통일하고 4Bit 셀은

하나의 WordLine이 공유되어야 하므로 가로로 길게

Poly를 연결했다. ([그림 33] 참고)

그리고 셀 위로 VDD, GND를 M3로 가로로

이어주었고, BL, BL’은 세로로 연결했다.

([그림 33] 참고)

셀의 WL을 ON/OFF 할 수 있는 Row Decoder는

왼쪽에 Column Decoder는 위쪽에 배치되어 있으므로

M3를 이용하여 Row Decoder의 출력을, M2를 이용하여

Column Decoder의 출력을 연결했다.

또한, 모든 Bit_Line들을 연결하기 위해 한 열에 하나씩 M3을 사용하여 모든 Bit_Line들을 각각 연결했다.

⓶ 5 to 32 Low Decoder

그림 37. 5 to 32 Decoder

1024*4Bit=4096 Bit Cell Layout 시

해당 총 면적이 1363um*1213um의 크기가 나왔다.

따라서 Decoder 설계를 진행할 때,

초기에 면적을 계산하고 설계를 진행했다.

1500um*1500um라는 칩 규정에 따라

최대한 가로를 얇게 설계해야 했으므로

2 to 4 Decoder를 위에 배치하고

나머지 3 to 8 Decoder 4개를 밑으로 이어주었다.

따라서 [그림 35]와 같이 가로 사이즈 30um로

5 to 32 디코더를 설계했다.

2 to 4 Decoder와 3 to 8 Decoder를 좀 더 자세하게

보면 밑에 그림과 같다.

그림 37. 5 to 32 Decoder

1024*4Bit=4096 Bit Cell Layout 시

해당 총 면적이 1363um*1213um의 크기가 나왔다.

따라서 Decoder 설계를 진행할 때,

초기에 면적을 계산하고 설계를 진행했다.

1500um*1500um라는 칩 규정에 따라

최대한 가로를 얇게 설계해야 했으므로

2 to 4 Decoder를 위에 배치하고

나머지 3 to 8 Decoder 4개를 밑으로 이어주었다.

따라서 [그림 35]와 같이 가로 사이즈 30um로

5 to 32 디코더를 설계했다.

2 to 4 Decoder와 3 to 8 Decoder를 좀 더 자세하게

보면 밑에 그림과 같다.

⓷ Precharge + Write_Driver + Sense_Amplifier + Tristate_Buffer

그림 38. Pre+Write+Sense+Tristate

⓷은 pre-charge, write_driver,

sense_amp, tristate Buffer를 하나로

합쳐놓은 셀의 사진입니다. ([그림 41 참고]

우선, Precharge는 PRE 신호와

WE 신호가 거의 동일시하게 들어오기 때문에

Layout 시 근접하게 설계하였습니다.

1Bit Cell의 BL, BL'의 간격이 4.4um 이므로

pre-charge, write-driver, sense-amp의

BL BL’의 간격 4.4um를 유지하며 Pre, Write,

Sense_Amp Layout을 진행했다.

마찬가지로 가로에는 M3만 이용하였고 세로에만

M2를 사용했고, VDD와 GND를 가로로 연결되기

용이하게 설계하였다.

'회로설계' 카테고리의 다른 글

| Verilog 기초 (0) | 2024.08.26 |

|---|---|

| RTL 디지털 설계 (VHDL) (0) | 2024.08.19 |

| EDA_cadence_VLSI_설계, 기초 단축키 (0) | 2024.08.01 |